Супервизоры напряжений для системных источников питания семейства WT751x

В схемотехнике современных системных источников питания, практически, обязательным становится такой элемент, как супервизор напряжений. Супервизор напряжений в большинстве случаев представляет собой отдельную микросхему, функцией которой является контроль выходных напряжений блока питания и генерация сигнала PowerGood . Кроме того, супервизор напряжений является тем элементом, который обеспечивает запуск и выключение блока питания. На сегодняшний день мировая электронная промышленность предлагает множество различных супервизоров напряжения, но одними из самых популярных при разработке блоков питания являются, несомненно, микросхемы семейства WT 751 x , выпускаемые компанией Weltrend Semiconductor .

Компанией Weltrend Semiconductor предлагается несколько типов супервизоров, как простых трехканальных, так и современных с расширенным набором функций по контролю выходных токов и напряжений. Сегодня мы обсудим самых младших представителей семейства WT 751 x , а именно супервизоры WT 7510, WT 7511 и WT 7512, которые являются простыми трехканальными супервизорами, контролирующими только величину основных выходных напряжений. Но, несмотря на свою простоту, эти микросхемы достаточно широко применялись и применяются в системных блоках питания.

Трехканальные супервизоры напряжений WT 751 x разработаны специально для системных блоков питания персональных компьютеров с целью уменьшения количества применяемых электронных компонентов и упрощения схемотехники управляющих каскадов. Данные микросхемы выполняют функции цепей защиты от превышения и от снижения выходных напряжений блока питания, функции формирователя сигнала Power Good (питание в норме), и функции контроля сигнала PSON (сигнал включения блока питания). Таким образом, применение данной микросхемы способно значительно упросить схемотехнику блока питания, так как супервизор напряжений заменяет собой целый ряд каскадов.

К особенностям микросхем семейства WT 751 x можно отнести:

– широкий диапазон питающих напряжений: от 4В до 15В;

– обеспечение защиты от превышения напряжений в каналах +5 V , +3.3 V и +12 V ;

– обеспечение защиты от снижения напряжений в каналах +5 V и +3.3 V ;

– наличие выхода с открытым коллектором для формирования сигнала защиты при ошибках в работе блока питания;

– наличие выхода с открытым коллектором для формирования сигнала Power Good (по состоянию напряжений +5 V и +3.3 V );

– обеспечение временной задержки в 300 мс при формировании сигнала Power Good ;

– обеспечение защиты от ложного срабатывания блока питания при возникновении “скачков” сигнала PS – ON в момент его активизации (защита обеспечивается в течение 38 мс);

– наличие встроенного подавителя помех при переключениях микросхемы (подавитель действует в течение 73 мкс);

– обеспечение временной задержки в 75 мс при срабатывании защиты от снижения напряжений;

– обеспечение временной задержки в 2.4 мс при выключении сигнала FPO сигналом PSON .

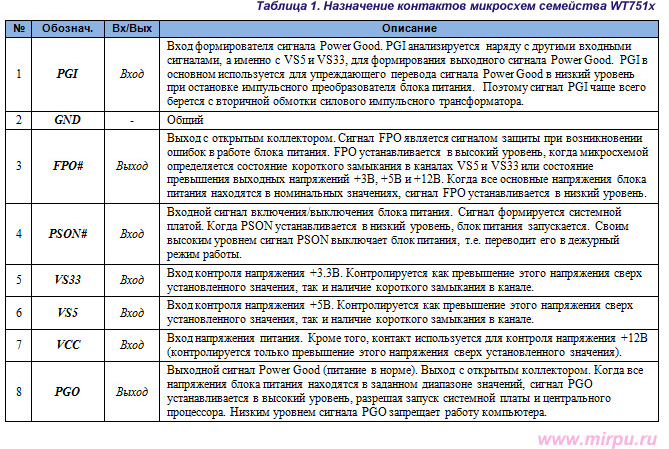

Цоколевка корпуса микросхемы представлена на рис.1, а описание ее контактов приводится в табл.1.

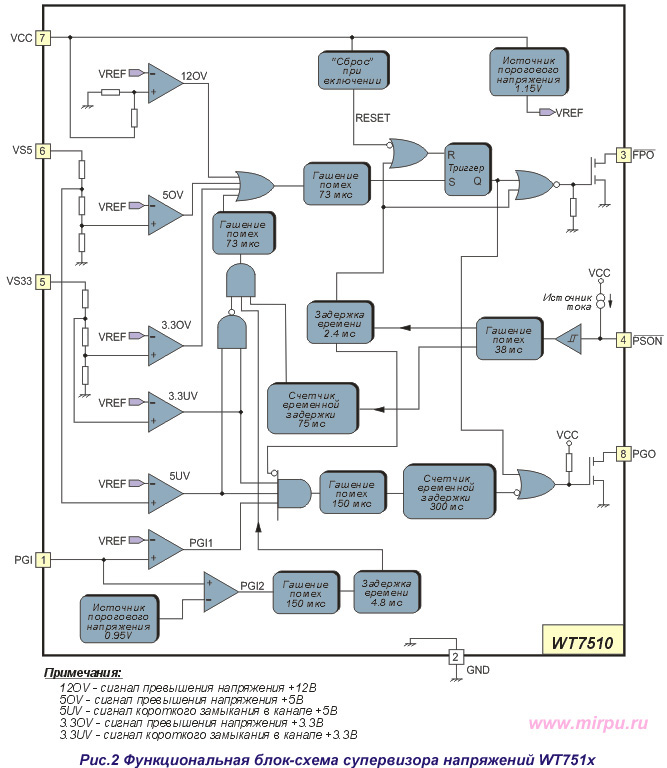

Функциональная блок-схема супервизора напряжений WT 751 x представлена на рис.2.

Рассмотрим основные принципы функционирования микросхем WT 751 x .

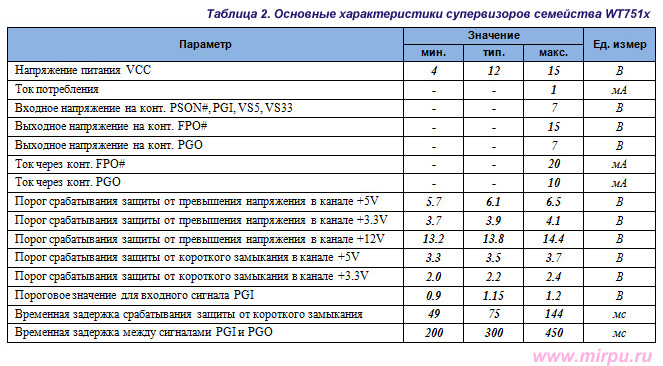

Основные характеристики супервизоров напряжений WT 751 x приводятся в табл.2.

Нормальное функционирование WT 751 x

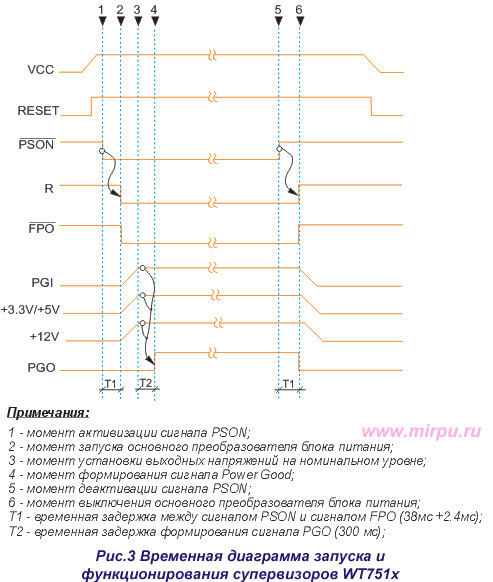

Временная диаграмма, поясняющая нормальное функционирование микросхем WT 751 x , представлена на рис.3. Как видно из диаграммы, в момент появления на входе микросхемы питающего напряжения VCC , ее внутренний сигнал RESET устанавливается в высокий уровень, разрешая функционирование всех внутренних компонентов супервизора. Установка сигнала RESET в высокий уровень происходит в момент, когда напряжение VCC достигнет величины 4В. Соответственно, и сброс сигнала RESET произойдет при снижении напряжения VCC до величины менее 4 В. Первоначально, напряжение VCC формируется дежурным источником питания, и, как правило, этим напряжением является +5 V _ SB .

В момент, когда системной платой формируется сигнал PSON # низкого уровня, должен начинаться процесс запуска основного преобразователя блока питания. Чтобы избежать случайного запуска блока питания при коротких просадках сигнала PSON , обеспечивается временная задержка величиной 38 мс. Только спустя это время внутренняя логика супервизора формирует сигнал, которым обеспечивается запуск всех внутренних компонентов и который переводит сигнал FPO # в низкий уровень.

Установка сигнала FPO # в низкий уровень должна приводить к запуску основного преобразователя блока питания. Как правило, сигналом FPO # управляется оптопара цепи запуска основного источника питания.

В момент запуска основного преобразователя все выходные напряжения блока питания (а значит и +3.3 V , +5 V и +12 V ) начинают плавно нарастать. К вторичной обмотке силового импульсного трансформатора подключена цепь формирования сигнала PGI , который получают выпрямлением импульсов ЭДС, наводимых в одной из вторичных обмоток трансформатора. Поэтому сигнал PGI также начинает плавно нарастать в момент запуска основного преобразователя. Когда все выходные напряжения блока питания, а также сигнал PGI достигнут номинальных значений, запустится внутренний счетчик, формирующий временную задержку 300 мс. И только спустя это время сигнал PGO на выходе микросхемы установится в высокий уровень, разрешая запуск микропроцессора на системной плате.

Когда системной платой сигнал PSON # устанавливается в высокий уровень, начинается отключение основного преобразователя. Опять же, чтобы избежать ложных срабатываний блока питания, обеспечивается временная задержка в 38 мс, только после истечения которой изменяется состояние сигналов FPO # и PGO . А именно, сигнал FPO # устанавливается в высокий уровень, выключая через оптопару основной преобразователь, а сигнал PGO сбрасывается в низкий уровень, запрещая работу системной платы и микропроцессора компьютера.

Функционирование WT7 51 x в аварийных режимах

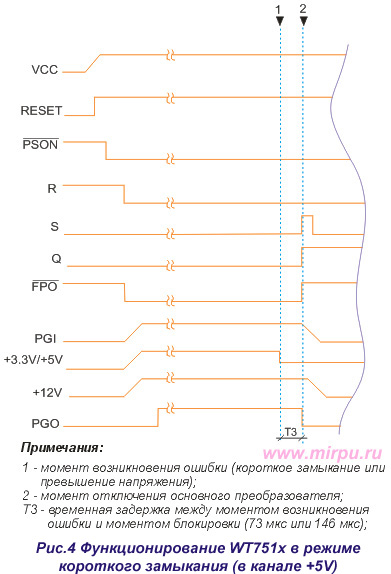

Во-первых, предположим, что во время работы блока питания происходит короткое замыкание в канале +5 V , и напряжение этого канала падает ниже 4В (временная диаграмма на рис.4). Это приводит к тому, что внутренний компаратор короткого замыкания генерирует сигнал 5 UV , который в итоге приводит к установке на входе триггера импульса S . Импульс S формируется с временной задержкой примерно 146 мкс (73мкс + 73 мкс). Активизация сигнала S , приводит к переключению триггера и установке на его Q -выходе высокого уровня, т.е. приводит к блокировке микросхемы. Триггер управляет состоянием сигнала FPO #, который переводится в высокий уровень, что приводит к остановке основного преобразователя и сбросу сигнала PGO в низкий уровень. Для сброса триггера и повторного запуска микросхемы необходимо выключить и снова включить микросхему.

В том случае, если происходит превышение выходных напряжений блока питания, блокировка микросхем WT 751 x происходит аналогичным образом, лишь только временная задержка при выключении будет составлять всего73 мкс.

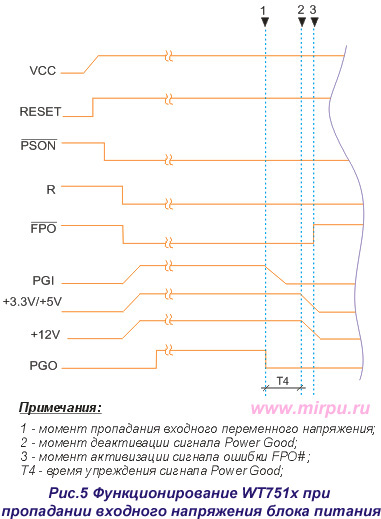

Во-вторых, рассмотрим ситуацию, когда пропадает входное напряжение блока питания (временная диаграмма на рис.5). В этом случае начинает уменьшаться напряжение сигнала PGI , который снимается с вторичной обмотки импульсного трансформатора. Напряжения +5 V , +3.3 V и +12 V продолжают удерживаться на номинальных уровнях за счет выходных конденсаторов большой емкости. Снижение уровня сигнала PGI практически сразу приводит к сбросу сигнала PGO ( Power Good ) в низкий уровень. Только через некоторый период времени, который определяется емкостью сглаживающих конденсаторов, начинается снижение выходных напряжений блока питания, что приводит к установке сигнала FPO # в высокий уровень. Т.е. состояние ошибки возникает уже после того, как сигнал Power Good запрещает работу центрального микропроцессора.

Диагностирование микросхем семейства WP 751 x

Упрощенная диагностика

Наиболее простым способом проверки микросхемы, является “прозвонка” ее основных контактов с целью выявления пробоя на корпус. Для этого необходимо измерить сопротивление между конт.2 ( GND ) и:

Все эти измерения должны показать очень большое сопротивление. В противном случае, можно говорить о неисправности микросхемы.

Функциональная диагностика

Функциональная диагностика проводится с целью выявления ошибок в работе микросхемы. Функциональную проверку проще всего осуществлять, не выпаивая микросхему. Наиболее простой является следующая проверка:

– от лабораторного источника питания (или от второго системного блока питания) подать напряжение +5В на контакт VCC (конт.7);

– при этом между контактом FPO # (конт.3) и контактом GND (конт.2) должно быть большое сопротивление, а на контакте PSON # (конт.4) должно установится напряжение 3.4В – 3.6В;

– далее соединяем контакт PSON # (конт.4) с GND и в этот момент времени между контактом FPO # (конт.3) и контактом GND (конт.2) сопротивление на очень короткий период времени должно стать малым (поэтому для измерения сопротивления необходимо использовать быстродействующие измерительные приборы).

Полная функциональная проверка

Для осуществления этой проверки лучше всего поступить следующим образом: тестируемый блок питания с микросхемой WT 751 x не включать в сеть, а не его выходы подать напряжения +5 V , +3.3 V , +12 V и +5 VSB от другого работоспособного блока питания, который включается в сеть и запускается. Таким образом, имитируется наличие всех выходных напряжений тестируемого блока питания. Однако при таком включении следует еще проанализировать и сигнал PGI . Если этот сигнал формируется из импульсов вторичной обмотки силового трансформатора, то на конт.1 микросхемы необходимо будет подать напряжение напрямую (с помощью перемычки) с канала +3.3 V . Собрав такой диагностический стенд и запустив его, тестируем выходные сигналы супервизора:

– при высоком уровне сигнала PSON # на выходе FPO # должен быть высокий уровень, а на выходе PGO – низкий.

– при подаче на контакт PSON # низкого уровня (перемычкой на корпус) на выходе FPO # устанавливается низкий уровень, а на выходе PGO – высокий;

– далее можно отключать от тестируемого блока питания отдельные напряжения (например, +5В) и контролировать изменение состояний сигналов FPO # и PGO .

Методика проверки может быть дополнена и расширена, исходя необходимости и возникающей неисправности блока питания. Для этого достаточно внимательно изучить материал настоящей публикации. – все определяется лишь инструментальным оснащением стенда и фантазией специалиста.

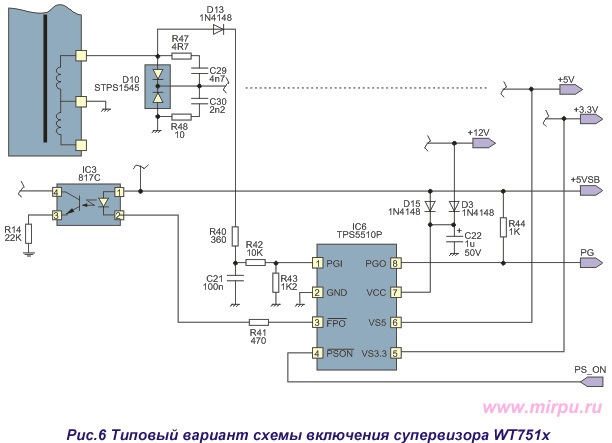

В качестве примера практического варианта применения микросхемы WT 7510 представляем принципиальную схему блока питания PowerMan IP – P 350 AJ . В данной схеме можно отметить несколько интересных моментов.

Во-первых, в данной схеме разработчики обеспечивают контроль не только напряжений +3.3В, +5В и +12В, но и отрицательных напряжений в каналах -5В и -12В. Отрицательные напряжения контролируются через вход V 33, который предназначен, в принципе, для контроля напряжения +3.3В. К этому входу дополнительно подключен транзистор Q 6, который открывается в случае возникновения коротких замыканий или при большой нагрузке в отрицательных каналах напряжений. Контроль тока в каналах отрицательных напряжений осуществляется с помощью сумматора напряжений, состоящего из R 66/ R 67/ R 62/ D 21. Этот сумматор обеспечивает суммирование отрицательных напряжений и напряжения канала +5В. Результатом суммирования является нулевое напряжение в средней точке резисторов R 62/ R 67. При возникновении короткого замыкания в отрицательном канале напряжение средней точки сумматора становится положительным, это приводит к открыванию транзистора Q 6 и шунтированию контакта V 33 на землю. Такое состояние интерпретируется микросхемой как короткое замыкание (снижение напряжения) в канале +3.3В, что приводит к блокировке супервизора и выключению источника питания.

Во-вторых, в схеме предусмотрен вариант упреждающего сброса в низкий уровень сигнала Power Good ( PGO ) при пропадании сетевого напряжения. Для этого импульсы, снимаемые с конт.5 силового импульсного трансформатора Т1, выпрямляются диодом D 14 и сглаживаются конденсатором C 36. Далее делитель R 46/ R 47 создает на контакте PGI (конт.1) напряжение, наличие которого горит о генерации импульсного преобразователя.

В-третьих, необходимо отметить, что в представленном блоке питания основной преобразователь построен по однотактной схеме. В подобных источниках питания запуск основного преобразователя очень часто осуществляется подачей питающего напряжения на микросхему ШИМ-контроллера после активизации сигнала PSON . Соответственно, выключение преобразователя происходит в момент, когда это питающее напряжение снимается с микросхемы. В рассматриваемой схеме подача питающего напряжения на ШИМ-контроллер ( U 1) осуществляется с помощью оптопары PC 1, которая, в сою очередь, управляется сигналом FPO супервизора. Перевод сигнала FPO в низкий уровень приводит к протеканию тока через светодиод оптопары PC 1, и, как следствие, к включению основного преобразователя.

И, наконец, питание микросхемы супервизора осуществляется напряжением +5 V _ SB в период, когда работает только дежурный источник питания. После запуска основного преобразователя, супервизор начинает питаться от канала +12 V через D 18.